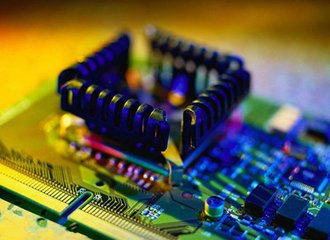

美国加州大学柏克莱分校(UCBerkeley)的科学家们表示已经找到一种可推动晶片电感器(on-chipinductor)技术进展的新方法,将有助于催生新一代微型射频(RF)电子与无线通讯系统设计。

加州大学的研究人员们深入探索在奈米磁铁(nanomagnet)中奈米材料合成的最新发展。根据加州大学柏克莱分校机械工程系教授LiweiLin表示,研究人员们发现,采用外覆绝缘层的磁性奈米粒子可使高频的晶片电感器尺寸缩小,同时提升性能,同时,「藉由其高截止频率提供良好的导磁率,从而降低在高频作业时的涡流损耗。」 工程师们经常面对的问题是,在试图缩减晶片电感器尺寸的同时,还得保持其最佳电感与性能。LiweiLin表示这些困难主要来自于「基本科学以及工程实践约束」所造成的限制。 晶片电感器技术并未发生像电晶体技术一样的进展电晶体技术在过去40年来一直遵循摩尔定律。电感器在电路上算是一款被动元件被归类于「超越摩尔定律」的领域,因此整合的是不会因摩尔定律而微缩的RF与MEMS等非数位化功能。 晶片电感器架构需要较大的面积,因为在其金属走线之间需要一定的长度、匝数、厚度与空间,以实现适当的电感与性能。然而,对于要求较大的面积则可能会因为在旋转线圈和半导体基板之间产生寄生效应而造成电感损失。 因此,电感器在微型化时必须添加磁性材料,但在这方面也带来其他的技术限制,「例如制程方案、相容于标准制程,以及材料的稳定度」,LiweiLin说,「磁性材料在磁导率和频率响应方面存在一些限制。」 新的电感器制造技术采用绝缘的奈米复合磁性物质作为填充材料来减少晶片电感器尺寸,以及提高达80%的电感,从而使晶片电感器缩减至少50%。此外,LiweiLin强调,它还具有使作业频率范围从GHz级扩展至10GHz的潜力。 他预计电感器技术的这些进展可望在未来3-5年内落实应用于晶片制程中。 |